# Study of 3-nm Cylindrical GAAFETs with Variations in High-k Dielectric Gate-oxide Materials

K.M. Ashraful Hoque Fahim

Department of Electrical and

Electronic Engineering

University of Liberal Arts

Bangladesh

Dhaka, Bangladesh

ashraful.hoque.ee@ulab.edu.bd

Md. Jubair Hasan Khalid

Department of Electrical and

Electronic Engineering

University of Liberal Arts

Bangladesh

Dhaka, Bangladesh

jubair.hasan.eee@ulab.edu.bd

Md. Zesun Ahmed Mia

Department of Electrical and

Electronic Engineering

University of Liberal Arts

Bangladesh

Dhaka, Bangladesh

zesun.ahmed@ulab.edu.bd

Mirza Rasheduzzaman

Department of Electrical and

Electronic Engineering

University of Liberal Arts

Bangladesh

Dhaka, Bangladesh

mirza.rasheduzzaman@ulab.edu.

bd

Abstract— Semiconductor devices using high k dielectric materials are widely adopted in memory and amplifier applications. Among the semiconductor devices gate all around-FET (GAAFET) is now the latest trend being used instead of other field effect transistors to serve the purpose of reducing the short channel effects (SCE). In this work, we examine the performance of a circular cross-section gate all around-field effect transistor (GAA-FET) with varying gate dielectric characteristics with highk dielectric oxide materials (Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, HfSiO<sub>4</sub>, SiO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>) across the 3-nm channel length. These simulations showed that even though the dielectric constant over the channel increases in value, both ION-IOFF ratio and transconductance upsurge. The obtained results indicated that raising the dielectric constant in a gate oxide reduces subthreshold slope (SS), increases amplification rate, and reduces threshold voltage (V<sub>TH</sub>) roll-off as well. The Silvaco TCAD ATLAS simulation was calibrated against experimental data from different works of literature. The higher the dielectric constant, the lower the SCEs. It is also found that TiO2 is dominating over the other materials selected for the simulation for a higher value of dielectric constant.

Keywords—high k dielectrics, SILVACO TCAD, GAAFET, cylindrical shaped

# I. INTRODUCTION

To improve the speed of devices, reduce cost and make them more efficient the fundamental object, the transistor needs to be scaled down to quantum scale from the existing measurement and only then Moore's law [1] will persist. Reduction of channel length, use of high k dielectrics, using multi-gate FETs and beyond instead of classical gate structures can help in achieving quantum scale operations. Nevertheless, the impediments in this endeavor are the short channel effects (SCEs) during the quantum scaling [2]. The operation of such scaled transistors is disrupted [3] due to the SCEs. Due to this, additional applications have a variety of drawbacks, such as drain-induced barrier lowering (DIBL), which can have a significant negative impact. Moreover, threshold voltage roll-off, rise in leakage current, hot carrier effect, and velocity saturation have detrimental effects as well [4]. Due to an electrostatic decoupling between the source and drain, DIBL renders the gate ineffective. If the current on/off ratio is reduced, the transistor cannot be totally turned off or there may be other complications. [5]. All these consequences result from lowering the threshold voltage. When the gate length is shortened, the current drive is

decreased, which results in a rise in the electric field strength within the drain and the source. The high magnitude of the electric field disrupts the proportional connection, which ultimately leads to velocity saturation and a drop in the current drive. If the channel length is reduced threshold voltage is lowered as well [6]. An increase in sub-threshold leakage current will eventually lead to an increase in the amount of power that is lost as heat. The primary factors that were discussed before contribute significantly to the poor performance of the planar structures. A variety of approaches have been explored in order to reduce the number of SCEs. One solution to this problem is to employ gate structures that are either multi-gate or modified. [7]. Several modified gates exist like SOI-FETs [8], double gate MOSFETs [9], Fin-FETs, triple gate [10], pi gate [11], omega gate [12], square gate GAAFETs [13], and cylindrical gate GAAFETs [14]. Double gate MOSFET [1] gives better electrostatic potential control than single gate MOSFET. Fin-FET gives better electrical control to lower leakage current and reduce SCEs as it becomes like a set of fins [11]. By 10-nm triple gate FETs give a high current driving capability as well as good gate control over the channel [15]. Pi gate structure improves electrostatic potential in the channel as the gate is grown into a buried oxide [16]. Omega gate is similar to GAA having good scaling down characteristics however it shows intense corner effects [17]. Square gate GAAFET lower the SCEs whereas it has corner effects as well [18]. Cylindrical GAAFET has outdone all previous gate structures having better electrostatic control and overcoming SCEs [7]. As a result, it is in a better position for scaling down the transistor and keeping Moore's law [1] sustained.

In this work, we have simulated several cylindrical-shaped GAAFETs using different gate oxide materials. The effects of the variation have been analyzed regarding the existing literature. Drain current vs. drain voltage, subthreshold slope (SS), transconductance ( $g_m$ ), on and off current and their ratio is found in Silvaco TCAD. The effects are demonstrated using different graphical representations and tables. TiO2 is dominant compared to other materials. However, given the cost, HfO2 is frequently utilized. Finding a relatively inexpensive material with adequate qualities will be a future focus of this research. To modify the transistor characteristics, physical factors like channel radius and oxide thickness including the oxide materials will be taken into account.

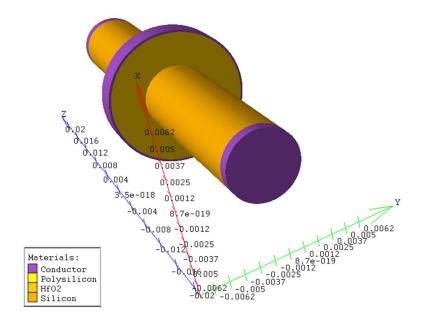

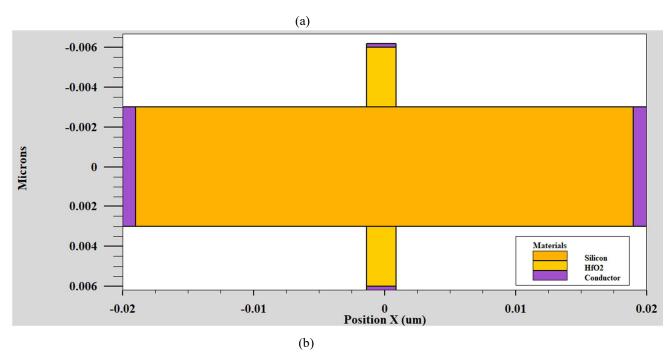

Fig.1 (a) 3nm Si-based GAAFET (b) Cross-sectional representation of different regions of 3nm Si-based GAAFET

### II. DEVICE STRUCTURE AND SIMULATION

# A. Device structures

Figures 1 show the simulated device structures and doping profiles of various regions of Silicon (Si) based 3nm gate all around Field Effect Transistor (GAAFET). This is the basic structure simulated in this paper. Several oxide materials with increasing dielectric constants are used to vary. The structures

are simulated using the corresponding parameters listed in table 2 from section B.

Table 1 [19] shows the static dielectric constants of materials used as gate oxides. Six oxide materials are chosen to simulate using existing literature [19]. The materials are varied while keeping the parameters from table 2 fixed to complete the simulation.

Our developed device is simulated using Silvaco TCAD Altas. Design specifications for the 3D cylindrical 3nm-GAAFET include a 3nm channel length (Lg), a 2nm channel radius (Rc), and a 3nm oxide thickness (tox). With a doping density of  $1\times10^{20}$  atoms/cm3, channel doping is done using concentrations of P-type doping. Once more, drain and source doping concentrations of  $1\times10^{16}$  atoms/cm³ are carried out using N-type doping concentrations. A 0.8 volt supply drain voltage and a 1-volt gate voltage are used.

#### B. Parameter tables

Table 1 Oxide materials used in structures

| Oxide Materials                | Di-Electric Constant (static) | $C_{ox} = Di	ext{-Electric}$<br>$Constant/t_{ox}$ |

|--------------------------------|-------------------------------|---------------------------------------------------|

| Al <sub>2</sub> O <sub>3</sub> | 9                             | 3                                                 |

| HfO <sub>2</sub>               | 25                            | 8.33                                              |

| HfSiO <sub>4</sub>             | 11                            | 3.67                                              |

| SiO <sub>2</sub>               | 3.9                           | 1.3                                               |

| Ta <sub>2</sub> O <sub>5</sub> | 22                            | 7.33                                              |

| TiO <sub>2</sub>               | 80                            | 26.67                                             |

Table 2 Parameters for designing 3nm Si-based GAAFETs for various gate-oxide materials comparison

| Design Parameters                             | Values                                    |

|-----------------------------------------------|-------------------------------------------|

| Channel Length, Lg                            | 3nm                                       |

| Channel Radius, R <sub>c</sub>                | 2nm                                       |

| Oxide Thickness, tox                          | 3nm                                       |

| Channel Doping Concentration, (P – type)      | 1×10 <sup>20</sup> atoms/ cm <sup>3</sup> |

| Drain / Source Doping Concentration, (N-type) | 1×10 <sup>16</sup> atoms/ cm <sup>3</sup> |

| Drain Voltage                                 | 0.8 V                                     |

| Gate Voltage                                  | 1 V                                       |

## III. RESULT AND FINDINGS

In this section, a comparison of several dielectric materials used as the gate oxide of a cylindrical GAAFET has been provided. The comparative results and their impacts are explored for a few applications.

#### A. Drain current characteristics

When the gate voltage is below the threshold voltage, the device is said to be in the "OFF state." Subthreshold current, which does not necessarily need to be in the "OFF state," is the current flow produced by the minority charge carriers. The ON current is started by the gate voltage, which is higher than the threshold voltage.

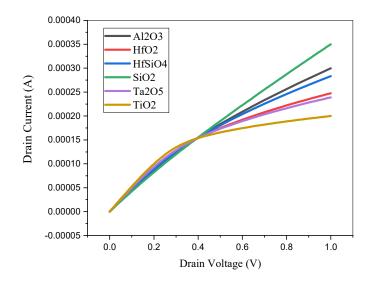

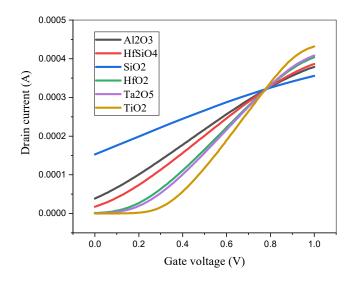

Drain current vs. drain voltage for different gate dielectric materials is shown in fig. 2. Fig. 3 shows the drain current of

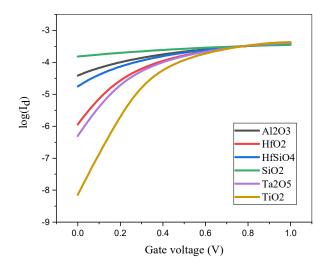

GAAFET for SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, HfSiO<sub>4</sub>, Ta<sub>2</sub>O<sub>5</sub>, and TiO<sub>2</sub> against gate-to-source voltages. From fig. 4 it can be observed that for HfO<sub>2</sub>, TiO<sub>2</sub>, and Ta<sub>2</sub>O<sub>5</sub> the leakage current is the same however for the rest of the dielectrics the leakage currents (OFF state current) are a little bit higher. With a low leakage current in SRAM applications, the signal-to-noise margin (SNM) increases. A better SNM might be obtained by employing high k dielectrics since their leakage current is lower.

Fig.2 I<sub>d</sub> vs V<sub>DS</sub> curve for different gate oxide materials

When the gate voltage is applied in Fig. 4, the drain current, which is below the threshold voltage, also rises. The logarithmic scale is used for the  $I_d$  vs.  $V_{\rm GS}$  displayed in Fig. 4. Thus, the increase in threshold voltage is seen. The drain current increases exponentially below the threshold voltage. The applied voltage of 0.7 V causes the current to stabilize. These changes may be compared using a subthreshold slope

Fig.3 I<sub>d</sub> vs V<sub>GS</sub> curve for different gate oxide materials

Fig. 4 log (I<sub>d</sub>) vs V<sub>GS</sub> curve for different gate oxide materials

# B. Subthreshold parameters

Subthreshold slope (SS)

$$SS = \left[\frac{d(log10Id)}{dVG}\right]^{-1}$$

....(1)

In the formula, VG = applied gate voltage and Id = resulting drain current

From table 3 we can observe that for TiO<sub>2</sub> the SS is lowest as the subthreshold voltage is low. For the other high k dielectrics, the characteristics of SS show a similar pattern as well. However, for Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, and HfSiO<sub>4</sub> the SS is comparatively high. Low subthreshold swing decreases the dissipated heat in devices having short channel lengths [7] which adds to the superior characteristics of TiO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, and HfO<sub>2</sub>.

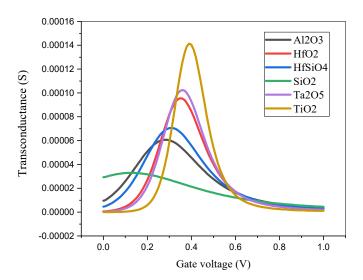

Transconductance (g<sub>m</sub>)

$$g_{\rm m} = \frac{d(Id)}{dVDS} \dots (2)$$

In fig. 5 transconductance vs gate voltage curve is shown. Transconductance determines the amplification rate of any device means the amount of drain current impacted by gate voltage [20]. From fig. 5 it can be observed that the amplification rate of  $TiO_2$  is the highest and the lowest is for  $SiO_2$ .

Table 3 shows that  $TiO_2$  has the lowest OFF current while having the highest ON current.  $SiO_2$  has a larger OFF current and a smaller ON current, on the other hand.  $TiO_2$  has a larger  $I_{on}$ - $I_{off}$  ratio than the other oxides as a result, whereas  $SiO_2$  has the lowest ratio.  $SiO_2$  has an on-to-off ratio that is almost ten times lower than  $Al_2O_3$ 's.  $TiO_2$  outperforms  $SiO_2$  in the ratio by

Fig. 5 g<sub>m</sub> vs V<sub>GS</sub> curve for different gate oxide materials

almost 10,000 times. The higher the  $I_{on}$ - $I_{off}$  ratio the greater the gate control we can exercise [21]. Table 3 further demonstrates that materials with high k dielectric constants have greater gate control abilities.

Table 3 g<sub>m</sub> vs V<sub>GS</sub> curve for different gate oxide materials

| Materials | Ion (A)    | Ioff (A)   | Ion/Ioff | SS       |

|-----------|------------|------------|----------|----------|

| Al2O3     | 2.63×10-05 | 6.78×10-07 | 38.7387  | 0.18719  |

| HfO2      | 2.74×10-05 | 2.59×10-08 | 1057.12  | 0.10726  |

| HfSiO4    | 2.67×10-05 | 2.65×10-07 | 100.519  | 0.15131  |

| SiO2      | 2.45×10-05 | 6.47×10-06 | 3.7905   | 0.58374  |

| Ta2O5     | 2.76×10-05 | 1.42×10-08 | 1939.99  | 0.1005   |

| TiO2      | 2.83×10-05 | 7.32×10-10 | 38681.2  | 0.078245 |

#### IV. CONCLUSION

This paper investigates the effect of variation in gate oxide materials for cylindrical-shaped gate all around FET using the gate length of 3 nm, oxide thickness of 2 nm, and channel radius of 2 nm. A higher on current is found with a higher dielectric constant as well as a lower off current is found with the higher dielectric constant. TiO<sub>2</sub> with the above combination is showing a higher drain current and high transconductance. Therefore devices having a higher dielectric constant in the oxide materials present superior features than the lower dielectrics as such higher on current, lower leakage current, higher amplification rate, and higher gate control ability. However, while having improved properties, materials with a higher dielectric constant are not cost-effective. The goal of this study in the future is to find a superior material with suitable qualities that is also affordable. Other physical characteristics will be considered in order to identify the right material and accomplish the required attributes. The factors that will be adjusted to achieve the aim are channel radius and oxide thickness.

#### REFERENCES

- [1] Moore, G. E. (1998). Cramming more components onto integrated circuits. *Proceedings of the IEEE*, 86(1), 82-85.

- [2] Young, K. K. (1989). Short-channel effect in fully depleted SOI MOSFETs. IEEE Transactions on Electron Devices, 36(2), 399-402.

- [3] Oh, S. H., Monroe, D., & Hergenrother, J. M. (2000). Analytic description of short-channel effects in fully-depleted double-gate and cylindrical, surrounding-gate MOSFETs. *IEEE electron device letters*, 21(9), 445-447

- [4] Park, J. T., & Colinge, J. P. (2002). Multiple-gate SOI MOSFETs: device design guidelines. *IEEE transactions on electron devices*, 49(12), 2222-2229.

- [5] Huang, W., Zhu, H., Wu, Z., Yin, X., Huo, Q., Jia, K., ... & Zhang, Y. (2020). Investigation of negative DIBL effect and miller effect for negative capacitance nanowire field-effect-transistors. *IEEE Journal of the Electron Devices Society*, 8, 879-884.

- [6] Minhaj, E. H., Esha, S. R., Adnan, M. M. R., & Dey, T. (2018, November). Impact of channel length reduction and doping variation on multigate FinFETs. In 2018 International Conference on Advancement in Electrical and Electronic Engineering (ICAEEE) (pp. 1-4). IEEE.

- [7] Agarwal, A., Pradhan, P. C., & Swain, B. P. (2019). Effects of the physical parameter on the gate all around FET. Sādhanā, 44(12), 1-7.

- [8] Sreenivasulu, V. B., & Narendar, V. (2021). Design insights into RF/analog and linearity/distortion of spacer engineered multi-fin SOI FET for terahertz applications. *International Journal of RF and Microwave Computer-Aided Engineering*, 31(12), e22875.

- [9] Dhiman, G., & Ghosh, P. K. (2017, August). Analytical modeling of threshold voltage for double gate MOSFET. In 2017 International Conference on Energy, Communication, Data Analytics and Soft Computing (ICECDS) (pp. 1584-1588). IEEE.

- [10] Pavanello, M. A., Cerdeira, A., Doria, R. T., Ribeiro, T. A., Ávila-Herrera, F., & Estrada, M. (2019). Compact modeling of triple gate junctionless MOSFETs for accurate circuit design in a wide temperature range. *Solid-State Electronics*, 159, 116-122.

- [11] Dutta, R., Konar, S. C., & Paitya, N. (2020). Influence of gate and channel engineering on multigate tunnel FETs: a review. Computational Advancement in Communication Circuits and Systems, 345-355.

- [12] Song, Y. S., Hwang, S., Min, K. K., Jang, T., Choi, Y., Yu, J., ... & Park, B. G. (2020). Electrical and thermal performances of omega-shaped-gate nanowire field effect transistors for low power operation. *Journal of nanoscience and nanotechnology*, 20(7), 4092-4096.

- [13] Kushwaha, P., Agarwal, H., Mishra, V., Dasgupta, A., Lin, Y. K., Kao, M. Y., ... & Hu, C. (2019, October). Modeling the Quantum Gate capacitance of Nano-Sheet Gate-All-Around MOSFET. In 2019 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S) (pp. 1-3). IEEE.

- [14] Mohan, C., Choudhary, S., & Prasad, B. (2017). Gate all around FET: An alternative of FinFET for future technology nodes. *Int. J. Adv. Res. Sci. Eng.*, 6(7), 563-569.

- [15] Wang, H., Liu, Y., Han, G., Shao, Y., Zhang, C., Feng, Q., ... & Hao, Y. (2017). Performance enhancement in uniaxially strained germanium—tin FinTFET: Fin direction dependence. *IEEE Transactions on Electron Devices*, 64(7), 2804-2811.

- [16] Das, S., Choudhury, A., Ghosh, S., Sarkar, S., Chanda, M., & De, S. (2017, March). Parameter modeling of linearly doped double gate MOSFET with high-k dielectrics. In 2017 Devices for Integrated Circuit (DevIC) (pp. 136-140). IEEE.

- [17] Hsieh, D. R., Lin, J. Y., Kuo, P. Y., & Chao, T. S. (2017). Comprehensive analysis on electrical characteristics of Pi-gate poly-Si junctionless FETs. *IEEE Transactions on Electron Devices*, 64(7), 2992-2998.

- [18] Gupta, N., Vohra, A., & Chaujar, R. (2016, August). Linearity performance of Gate Metal Engineered (GME) Omega gate-silicon nanowire MOSFET: a TCAD study. In 2016 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC) (pp. 208-211). IEEE.

- [19] Robertson, J. (2004). High dielectric constant oxides. The European Physical Journal-Applied Physics, 28(3), 265-291.

- [20] Karbalaei, M., Dideban, D., & Heidari, H. (2020). Impact of high-k gate dielectric with different angles of coverage on the electrical characteristics of gate-all-around field effect transistor: A simulation study. *Results in Physics*, 16, 102823.

- [21] Zhang, W., Ragab, T., & Basaran, C. (2019). Electrostatic doping-based All GNR tunnel FET: an energy-efficient design for power electronics. *IEEE Transactions on Electron Devices*, 66(4), 1971-1978.